(C) Copyright: Angstrem, 2001-2003.

http:/www.angstrem.ru E-mail: market@angstrem.ru

All rights reserved. No part of this publication may be reprodused, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of ANGSTREM

# **FUNCTION**

- Character type dot matrix LCD controller and driver

- Easy Interface with 4-bit or 8-bit microprocessors

- · Wide range of various instruction functions

- Standard and extended operation modes for applications flexibility

- Mask programming of extended functions in standard/extended modes according to the Order Form

- · Mask programming of the desired customer's characters table

- 1 line of 5x8 or 5x11 dot or 2 lines of 5x8 dot characters display

- Chip and Mode Identifier allows to detect chip version and current state of controller

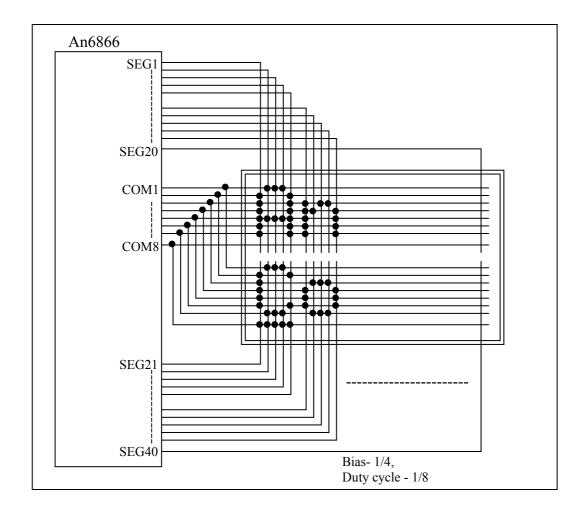

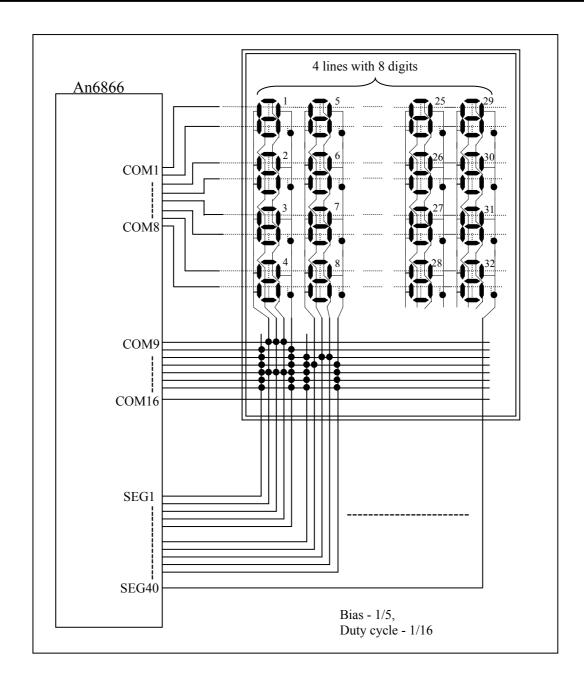

- Internal driver: 16 common and 40 segment signal outputs

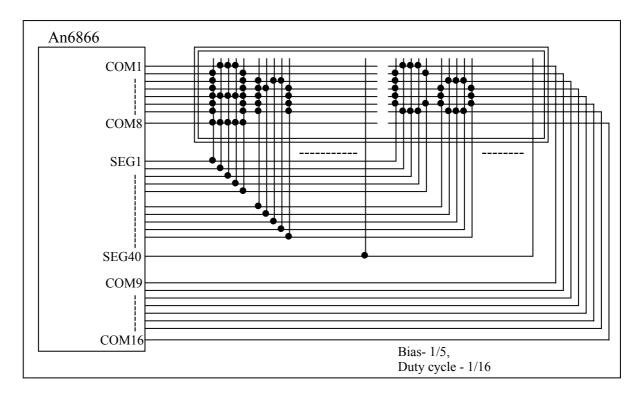

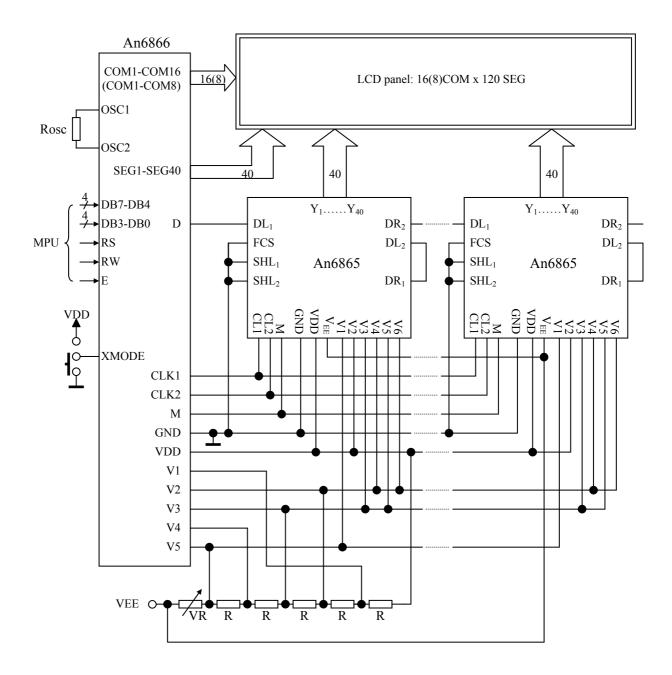

- Interface with the An6865 or An6863 extension driver to increase number of displayed characters (up to 80)

- Build-in automatic power-on reset function

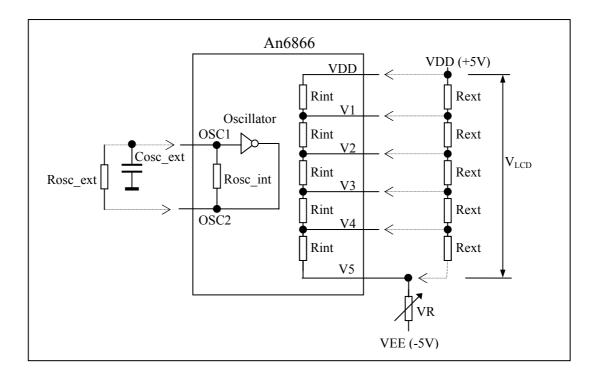

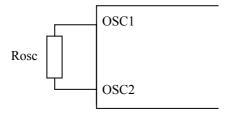

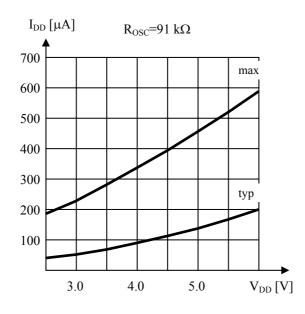

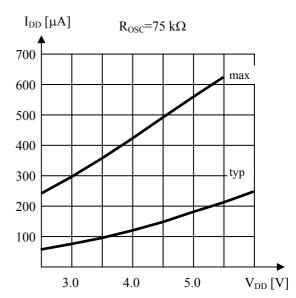

- · Internal oscillator with one external resistor

- Chip version configured with on-chip LCD supply voltage bias resistors and a clock oscillator resistor (no additional external elements)

## **FEATURES**

- Power Supply Voltage: 2.7V to 5.5V

- LCD Driving Voltage: 3.0V to 13V

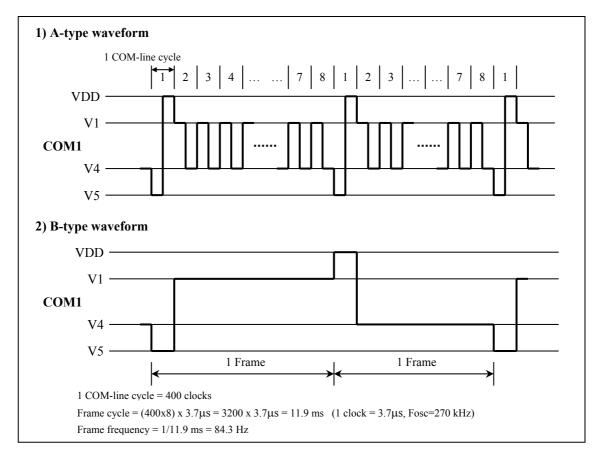

- Two types of Display Waveforms:

- A-type (line inversion)

- B-type (frame inversion)

- High-speed MPU bus interface 2 MHz (at 5V Power Supply)

- Display Data RAM size is 80 x 8 bits for 80 characters

- Character Generator ROM size is 19840 bits with two pages:

- 2 pages with 240 characters of 5x8 dot format for each or

- 1 page with 240 5x11 dot characters or

- combination of 2 pages region with 5x8 dot characters and 1 page region with 5x11 dot characters

- Character Generator RAM size is 64 x 8 bits for:

- 8 characters of 5x8 dot format or

- 4 characters of 5x11 dot format

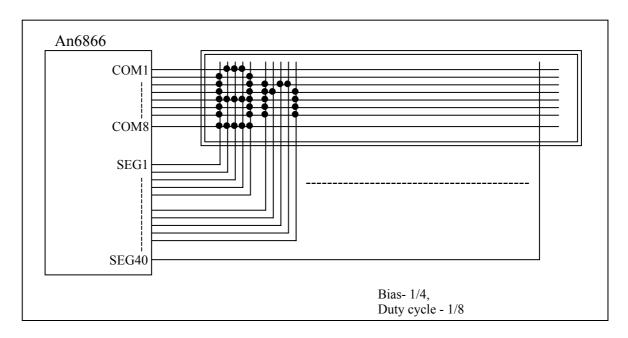

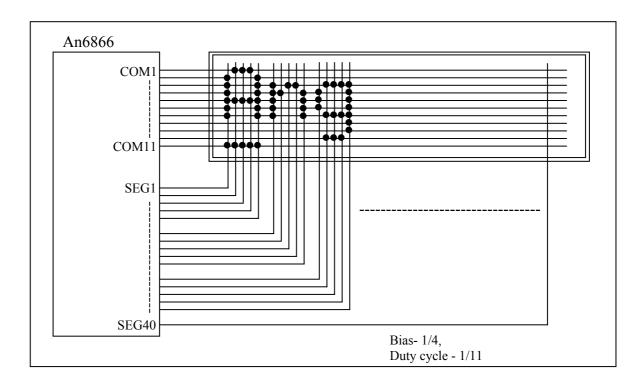

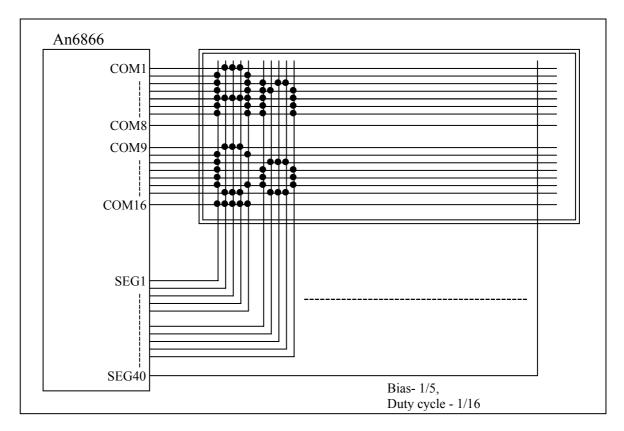

- Programmable duty cycle:

- 1/8 duty for one line of 5x8 dot characters

- 1/11 duty for one line of 5x11 dot characters

- 1/16 duty for two lines of 5x8 dot characters

- Low power consumption

### **Ordering Information**

| Version      | Description                                                               |

|--------------|---------------------------------------------------------------------------|

| An6866-xxyy  | Controller version with full function set for Standard and Extended modes |

| An6866S-xxyy | Controller version only for Standard mode (XMODE=1 or NC)                 |

Note:

xx - Functional mask option number,

yy - CGROM pattern number

### INTRODUCTION

The An6866 is a dot matrix LCD controller designed for display of alphanumeric data. It has standard compatible mode and extended mode with larger CGROM size and additional service functions.

The An6866 has 16 COM and 40 SEG outputs to display one 5x8 or 5x11 dot character line, or two 5x8 dot character lines. With internal segment outputs the controller can display up to 8 characters in each line (up to 16 characters in two-line mode). Extension drivers increase number of displayed characters to 80 (up to 40 characters in a line for two-line mode).

The displayed character codes are written into the 80-byte Display Data RAM (DDRAM). Character patterns are stored in the 19,840-bit Character Generator ROM (CGROM) or 64x8-bit Character Generator RAM (CGRAM). The CGROM capacity allows to code two pages of 5x8 dot characters or one 5x11 dot character page (up to 248 characters on each page). Mixed format coding is also allowed. In the CGRAM the user can write eight 5x8 dot characters or four 5x11 dot characters

Data exchange with an external control device is performed by an easy-to-use system interface compatible with many MPU types. Also the controller has a wide instruction set. Instructions and data can be transferred via 4- or 8-bit data bus. The An6866 features an advanced 4-bit interface that allows synchronization of the internal controller state with the interface timing diagram.

The An6866 has a standard extension driver interface with An6865, An6863 and similar type drivers. COM and SEG waveforms can be "A" or "B" type, as selected in the Order Form.

Reset function initializes the controller automatically after power on.

The An6866 has a Chip and Mode IDentifier (CMID), that allows the external MPU to detect chip version, ROM code and service functions status, as well as the current operation mode, and to adjust the system operating according to received data.

The controller is fabricated by the production single-metal CMOS technology. Mask programming of the CGROM, as well as initialization state, and the extended functions selection, are implemented by metal mask.

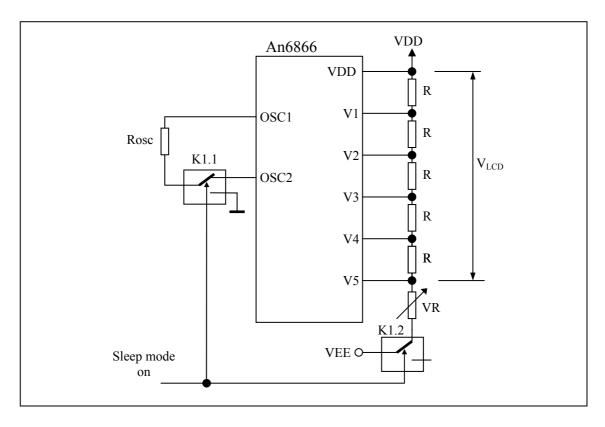

The controller IC contains on-chip LCD supply voltage bias resistors and a clock oscillator resistor. Whether the on-chip resistors should be connected as well as their nominal resistances are selected by the customer when making an order for a mask option.

Therefore, the An6866 features two base operation modes\*):

- 1) The Standard compatible mode with basic function set. This mode is enabled when the XMODE pin is either not connected or set to the logic "1" state.

- 2) The Extended mode, allows to use extended functions. This mode is enabled when the XMODE pin is connected to GND or set to the logic "0" state. The extended functions include the use of two CGROM pages for 5x8 dot characters, the Display Inversion control capability, the cursor blinking mode (similar to the PC text mode cursor).

- \*) Note: Standard and Extended functions as well as CGROM character coding and the initial state after power on can be selected by the Customer when filling in the Order Form. Some functions can be made accessible in the Standard mode, others in the Extended mode. Certain functions can be accessible in both modes or disabled (see Order Form).

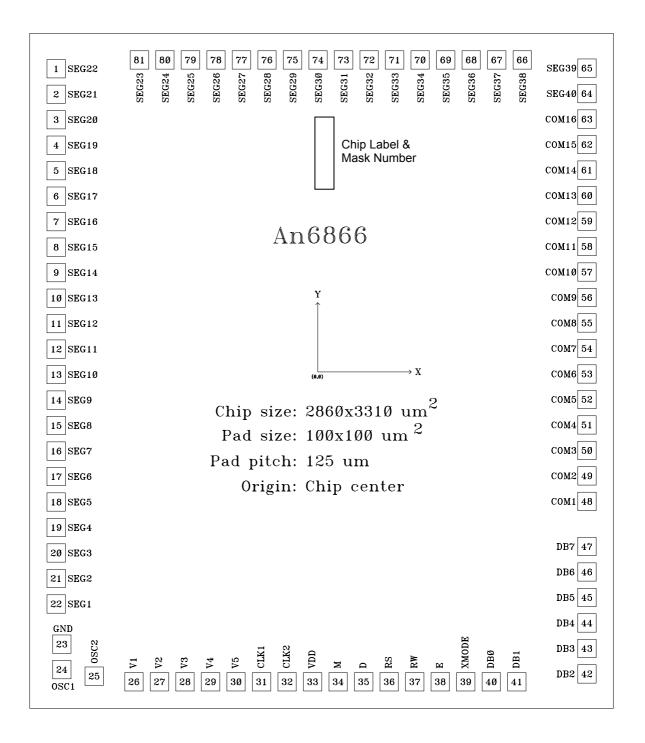

# **PAD DIAGRAM**

# **PAD LOCATION COORDINATES**

| Dad No | Pad Name | Coor    | dinates  | Dad No | Dad Nama | Coord      | dinates    |

|--------|----------|---------|----------|--------|----------|------------|------------|

| Pad No | Pau Name | X (µm)  | Y (µm)   | Pad No | Pad Name | X (µm)     | Y (µm)     |

| 1      | SEG22    | 135.0   | 3136.9   | 42     | DB2      | 2725.0     | 168.7      |

| 2      | SEG21    | 1       | 3011.9   | 43     | DB3      | 1 ,        | 293.7      |

| 3      | SEG20    | <b></b> | 2886.9   | 44     | DB4      | † <b>f</b> | 418.7      |

| 4      | SEG19    |         | 2761.9   | 45     | DB5      | 1          | 543.7      |

| 5      | SEG18    |         | 2636.9   | 46     | DB6      | 1          | 668.7      |

| 6      | SEG17    |         | 2511.9   | 47     | DB7      | 1          | 793.7      |

| 7      | SEG16    |         | 2386.9   | 48     | COM1     | T          | 1015.0     |

| 8      | SEG15    |         | 2261.9   | 49     | COM2     | 1          | 1140.0     |

| 9      | SEG14    |         | 2136.9   | 50     | COM3     | T          | 1265.0     |

| 10     | SEG13    |         | 2011.9   | 51     | COM4     | T          | 1390.0     |

| 11     | SEG12    |         | 1886.9   | 52     | COM5     | 1          | 1515.0     |

| 12     | SEG11    |         | 1761.9   | 53     | COM6     | 1          | 1640.0     |

| 13     | SEG10    |         | 1636.9   | 54     | COM7     | 1          | 1765.0     |

| 14     | SEG9     |         | 1511.9   | 55     | COM8     | 1          | 1890.0     |

| 15     | SEG8     |         | 1386.9   | 56     | COM9     | 1          | 2015.0     |

| 16     | SEG7     |         | 1261.9   | 57     | COM10    | 1          | 2140.0     |

| 17     | SEG6     |         | 1136.9   | 58     | COM11    | 1          | 2265.0     |

| 18     | SEG5     |         | 1011.9   | 59     | COM12    | 1          | 2390.0     |

| 19     | SEG4     |         | 886.9    | 60     | COM13    | 1          | 2515.0     |

| 20     | SEG3     |         | 761.9    | 61     | COM14    | 1          | 2640.0     |

| 21     | SEG2     | <b></b> | 636.9    | 62     | COM15    | 1          | 2765.0     |

| 22     | SEG1     |         | 511.9    | 63     | COM16    | 1          | 2890.0     |

| 23     | GND      | 162.9   | 314.8    | 64     | SEG40    | <b>†</b>   | 3015.0     |

| 24     | OSC1     | 162.9   | 189.8    | 65     | SEG39    | 1          | 3140.0     |

| 25     | OSC2     | 316.3   | 162.9    | 66     | SEG38    | 2412.6     | 3175.0     |

| 26     | V1       | 511.0   | 135.0    | 67     | SEG37    | 2287.6     | 1 .        |

| 27     | V2       | 636.0   |          | 68     | SEG36    | 2162.6     | <b>↑</b> • |

| 28     | V3       | 761.0   | 1 ∱      | 69     | SEG35    | 2037.6     | 1 1        |

| 29     | V4       | 886.0   | ]        | 70     | SEG34    | 1912.6     | 1          |

| 30     | V5       | 1011.0  | ]        | 71     | SEG33    | 1787.6     |            |

| 31     | CLK1     | 1136.0  |          | 72     | SEG32    | 1662.6     |            |

| 32     | CLK2     | 1261.0  |          | 73     | SEG31    | 1537.6     |            |

| 33     | VDD      | 1386.0  | ]        | 74     | SEG30    | 1412.6     |            |

| 34     | М        | 1511.0  | ]        | 75     | SEG29    | 1287.6     |            |

| 35     | D        | 1636.0  | ]        | 76     | SEG28    | 1162.6     |            |

| 36     | RS       | 1761.0  | ]        | 77     | SEG27    | 1037.6     |            |

| 37     | RW       | 1886.0  | ]        | 78     | SEG26    | 912.6      |            |

| 38     | E        | 2011.0  | ]        | 79     | SEG25    | 787.6      | _          |

| 39     | XMODE    | 2136.0  | ]        | 80     | SEG24    | 662.6      | _          |

| 40     | DB0      | 2261.0  | <u> </u> | 81     | SEG23    | 537.6      |            |

| 41     | DB1      | 2386.0  | <b>'</b> |        |          |            |            |

# **PIN DESCRIPTION**

| Pin Name     | Lines | Input/output                              | Description                                                   | Interface   |  |  |  |

|--------------|-------|-------------------------------------------|---------------------------------------------------------------|-------------|--|--|--|

| $V_{DD}$     | 1     |                                           | Positive voltage for logical circuit and LCD                  | Power       |  |  |  |

| <b>V</b> DD  | '     | <u>-</u>                                  | drivers                                                       | supply      |  |  |  |

| GND          | 1     | _                                         | Ground (0V)                                                   | Power       |  |  |  |

| OND          | '     | -                                         | Ground (0V)                                                   | supply      |  |  |  |

|              |       |                                           | Bias voltage level for LCD driving from                       |             |  |  |  |

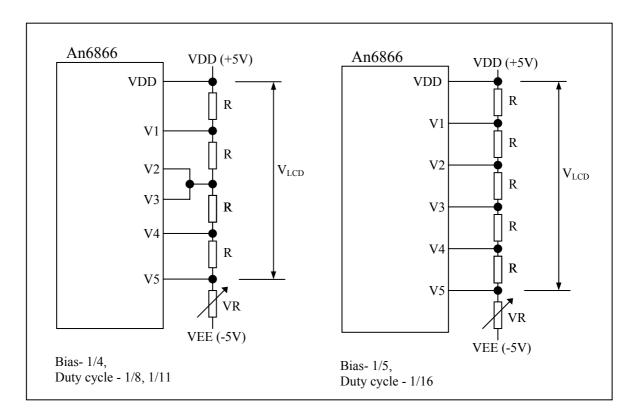

| V1 - V5      | 5     | _                                         | Power supply or resistive divider:                            | Power       |  |  |  |

| V 1 V 0      |       |                                           | $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5.$             | supply      |  |  |  |

|              |       |                                           | $V_5$ – negative bias voltage: $V_{DD}$ - $V_5$ = $V_{LCD}$ . |             |  |  |  |

| COM1 - COM16 | 16    | output                                    | Common signal outputs for LCD driving                         | LCD         |  |  |  |

| SEG1 - SEG40 | 40    | output                                    | Segment signal outputs for LCD driving                        | 202         |  |  |  |

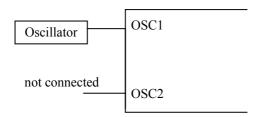

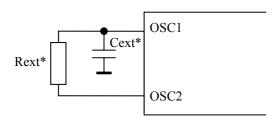

|              |       |                                           | When using internal oscillator, connect                       | external    |  |  |  |

| OSC1, OSC2   | 2     | input OSC1                                | external resistor.                                            | resistor or |  |  |  |

| 0001, 0002   | _     | output OSC2                               | If external clock is used, connect it to                      | external    |  |  |  |

|              |       |                                           | OSC1 (OSC2 open).                                             | oscillator  |  |  |  |

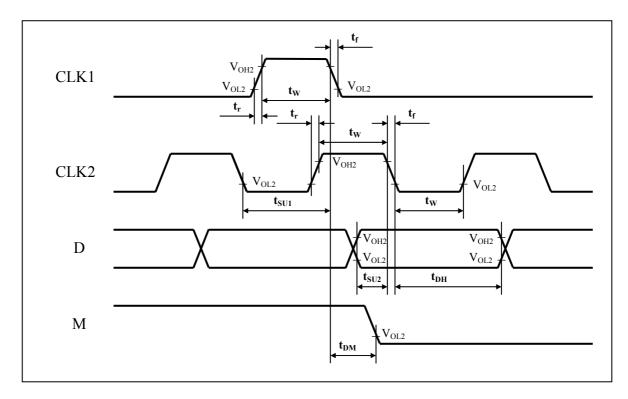

| CLK1         | 1     | output                                    | Extension driver latch clock                                  |             |  |  |  |

| CLK2         | 1     | output                                    | Extension driver shift clock                                  | Extension   |  |  |  |

| M 1          |       | The alternating signal to change polarity |                                                               |             |  |  |  |

| IVI          | '     | σαιραι                                    | of LCD driver voltage.                                        | driver      |  |  |  |

| D            | 1     | output                                    | Output extension driver data.                                 |             |  |  |  |

|              |       |                                           | Used as Interface register selection input.                   |             |  |  |  |

|              | 1     | input<br>(pull-up to V <sub>DD</sub> )    |                                                               |             |  |  |  |

| RS           |       |                                           | When RS=0 Instruction register is                             |             |  |  |  |

|              |       | (pail-ap to v <sub>DD</sub> )             | selected (when writing) or Busy flag state                    |             |  |  |  |

|              |       |                                           | and current address (when reading).                           |             |  |  |  |

|              |       | input                                     | Used as read/write selection input.                           |             |  |  |  |

| RW           | 1     | (pull-up to V <sub>DD</sub> )             | When RW=1 - reading operation                                 |             |  |  |  |

|              |       | (pull-up to VDD)                          | When RW=0 – writing operation.                                |             |  |  |  |

| E            | 1     | input                                     | Used as read/write enable signal.                             | MPU         |  |  |  |

|              |       | input / output                            | Used as low order bi-directional data bus,                    |             |  |  |  |

| DB0 - DB3    | 4     | (pull-up to V <sub>DD</sub> )             | when 8 bit bus mode. Not used, when 4-                        |             |  |  |  |

|              |       | (pull-up to VDD)                          | bit bus mode.                                                 |             |  |  |  |

|              |       |                                           | Used as high order bi-directional data                        |             |  |  |  |

|              |       | input / output                            | bus, when 8-bit bus mode. Used as both                        |             |  |  |  |

| DB4 - DB7    | 4     | (pull-up to V <sub>DD</sub> )             | high and low order, when 4-bit bus mode                       |             |  |  |  |

|              |       | (pull-up to VDD)                          | pins are.                                                     |             |  |  |  |

|              |       |                                           | DB7 used for Busy flag output.                                |             |  |  |  |

|              |       | input                                     | Used as operation mode switch signal:                         | MPU or      |  |  |  |

| XMODE        | 1     | (pull-up to V <sub>DD</sub> )             | XMODE=1 – standard mode,                                      | control     |  |  |  |

|              |       | (pail-ap to vDD)                          | XMODE=0 – extended mode.                                      | circuit     |  |  |  |

## **FUNCTIONAL DESCRIPTION OF AN6866**

#### 1. OVERVIEW

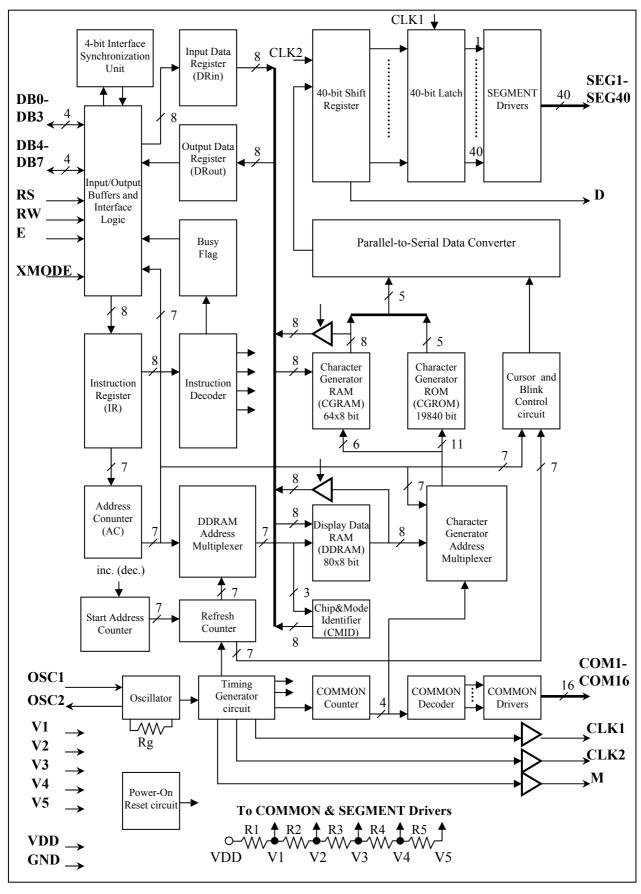

The An6866 internally provides all necessary functions to display characters. The chip includes interface with MPU, DDRAM, CGRAM and CGROM, LCD drivers and extended drivers interface to increase number of displaying characters. This controller allows to build information displaying systems with minimum of external components. It is possible to display one line with 5x8 or 5x11 characters or two lines with 5x8 characters.

Block Diagram is shown in Figure 1.

The An6866 is controlled by instructions from MPU interface. The Interface contains 8-bit data bus DB[7..0], interface operation enable pin (E), read/write mode pin (RW), data register or instructions register select pin (RS).

The controller can interface with MPU by two ways:

- by using 8-bit data bus and 3 control signals (totally 11 interface lines);

- by using 4 high-order bits of data bus (totally 7 interface lines), thus 4-bit data transferred twice (with two E pulses). For increase reliability of data transferring special synchronization mechanism for 4-bit groups is used.

The controller is operated through 2 input buffer registers: IR (Instruction Register) and DR (Data Register). Instructions and data are written into the selected register with E fall, then interface is locked out for the instruction execution time. Instructions are executed according to internal timing diagram independently of interface functioning. Busy Flag (BF) is used to check the state of current instruction execution. Before sending the next instruction to the controller, the MPU must check BF and make sure that previous instruction is finished and input registers are open for new data and instructions.

This interface model allows to operate with high-frequency bus independently from slow internal timing diagram of the controller, which forms internal cycles of instruction executing, memory access and display waveform.

Each instruction execution is accompanied with data reading from internal memory into output Data Register (DR). MPU can read this data by the next Data Read instruction.

The controller has 4 classes of instructions:

- designate controller functions (Function Set, Entry Mode Set, Display Clear, Display on/off, Cursor on/off, Blinking on/off);

- set internal RAM addresses (Set DDRAM/CGRAM Address, Return Home);

- perform data reading/writing operations with internal memory:

- perform miscellaneous functions.

Controller contains 3 memory units:

- DDRAM: contains codes of displayed characters (80 bytes). Character order in DDRAM corresponds to character order on LCD;

- CGROM: contains font table. CGROM contains up to 240 (248) characters at code range 16 (8) to 255. Coding of 5x8 or 5x11 dot characters is available, 5x8 dot characters may be allocated in two pages.

- CGRAM with 64-byte capacity for user characters (totally 8 characters 5x8 dots or 4 characters 5x11 dots). CGRAM occupies 16 (8) character codes from 0 to 15 (7). If CGRAM or its part is not used for user characters, it may be used as general purpose RAM.

Chip and Mode Identifier (CMID) allows external device to read type, chip version and current state of the controller. CMID allows to increase system functionality and reliability.

Controller memory (DDRAM or CGRAM) is allocated according to the current address stored in Address Counter (AC). It means that before random access to memory, it is necessary to write Set CGRAM/DDRAM Address instruction. After execution of any read/write instruction, AC address automatically changes by 1. Direction of AC address change depends on "ID" control bit of Entry Mode Set instruction.

Address Counter also defines cursor position on LCD.

The controller also has mode in which data write combines with display shift. It means that character code writing into DDRAM, address autoincrement and display backward shift take place simultaneously. Visually the cursor is stable and the character line is shifting. This mode is enabled by "S" control bit of "Entry mode Set" instruction.

Autoincrement feature allows to simplify controller programming for end-user applications.

DDRAM addressing depends on display format. In 1-line mode, single address range from 0 to 79 for all 80 characters is used. In 2-line mode, DDRAM address is divided into two ranges: from 0 to 39 for the first line and from 64 to 103 for the second line. When sequential incrementing or decrementing of AC address counter, DDRAM address passes both ranges, accordingly the cursor moves from the first line to the second and vice versa.

Character code read from DDRAM during display refresh time is used to select its pattern from the CGROM or CGRAM. Data from Character Generator is transformed to sequential form and written into SEG shift register at each CLK2 strobe. When SEG shift register if filled with data for the next COM (display row), data is transferred from shift register to SEG outputs latches at CLK1 strobe synchronously with switching to the next COM, and data appears in all driver outputs and on the LCD.

The controller has 40 SEG (display column) drivers for displaying first 8 characters per line. To increase number of displayed characters, it is possible to use extension drivers such as An6865 (40 SEG) or An6863 (80 SEG). Extension drivers are connected to the controller through driver interface, which contains 4 outputs:

- CLK2 data shift strobe,

- CLK1 data latch strobe.

- D serial data output for shift register extension,

- M alternating signal for polarity change of LCD voltage.

Figure 1. An6866 Block Diagram.

Functional diagram can be divided into the following parts:

#### 1) Logic control circuit:

- MPU bus interface,

- Instruction decoder,

- Address Counter (AC),

- Start Address Counter,

- Oscillator and Timing generator,

- Timers for COM cycle and character/cursor blinking,

- Cursor forming circuit,

- Power-on Reset circuit.

#### 2) Memory circuit:

- Display Data RAM (DDRAM),

- Character Generator RAM (CGRAM),

- Character Generator ROM (CGROM),

- Chip and Mode Identifier (CMID),

- Memory access control circuits, address and data multiplexer.

# 3) LCD drivers circuit with voltage level shift:

- Parallel-to-serial data converter for transfer Character Generator data to SEG shift register,

- COM counter & decoder,

- COM drivers,

- SEG shift register and output latches,

- SEG drivers,

- Extension drivers interface.

#### 2. LOGIC CONTROL CIRCUIT

#### 2.1. MPU bus interface

Interface registers

The An6866 has two 8-bit interface registers: instruction register (IR) and data register (DR). Instruction register is write-only and it stores instruction codes. Data register is read/write (write – DRin, read – DRout). Data exchange between registers and MPU perform through bi-directional Data Bus (DB).

Registers are selected by RS signal, and read/write operations are selected by RW signal (refer to table 1).

Table 1 Interface Register selection

| RS | RW | Operation                                             |

|----|----|-------------------------------------------------------|

| 0  | 0  | Writing instructions into IR                          |

| 0  | 1  | Reading Busy Flag (DB7) and Address Counter (DB6-DB0) |

| 1  | 0  | Writing data into DR                                  |

| 1  | 1  | Reading data from DR                                  |

The IR register is used to store instruction code while instruction executing.

The DR register is used for temporary storage of data to be read/write to DDRAM or CGRAM. While executing any instruction RAM data always is read automatically, thus DRout always contains data from the last address (even if the address was changed during instruction execution). This data can be read from DB-bus by the next read instruction. It is guaranteed that MPU always receives data from the last address.

The main function of interface registers is separating MPU interface timing diagram from internal controller timing diagram. IR and DR registers allow to release MPU data bus during instruction execution. While instruction execution, registers are locked, and information in registers can not be changed.

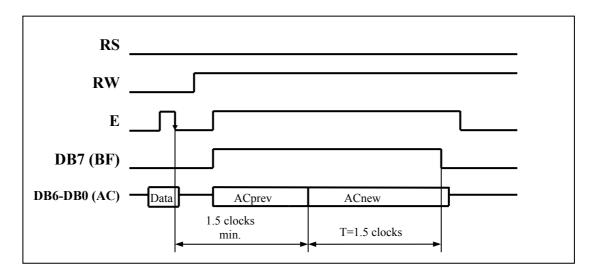

Busy Flag (BF)

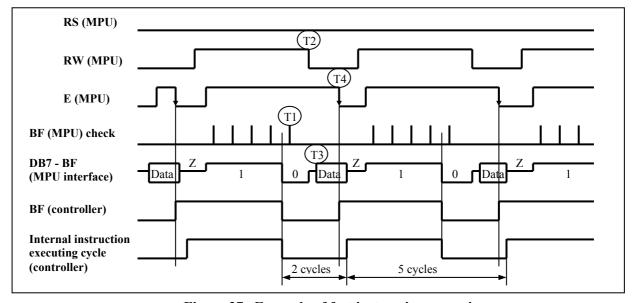

Before writing the next instruction, MPU must ensure that previous instruction is completed and interface registers are free. To make this, MPU can check Busy Flag (BF). If BF=1, the controller is executing the previous instruction, and MPU must perform idle cycles or other operations. The next instruction must be written after ensuring that BF is "0".

Busy Flag is read when RS=0 and RW=1 at DB7 pin (see Table 1). Reading BF procedure is used only for checking controller state and it is not an instruction, i.e. it does not lock input registers.

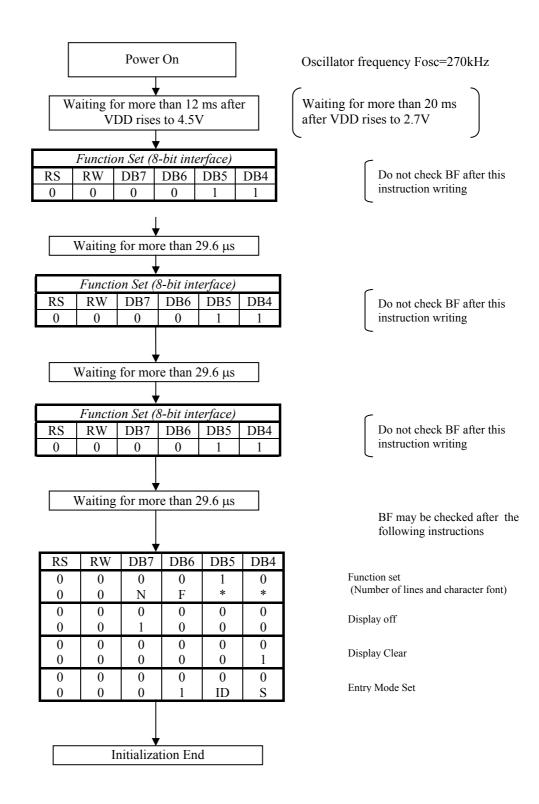

4- and 8-bit interface bus

The An6866 can operate with 4- or 8-bit interface bus. Bus width is selected by DL bit of Function Set instruction (see part 2.10).

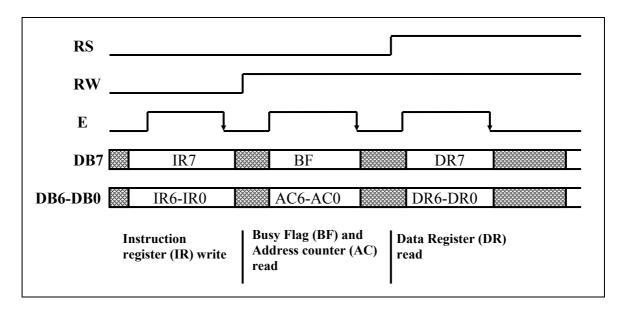

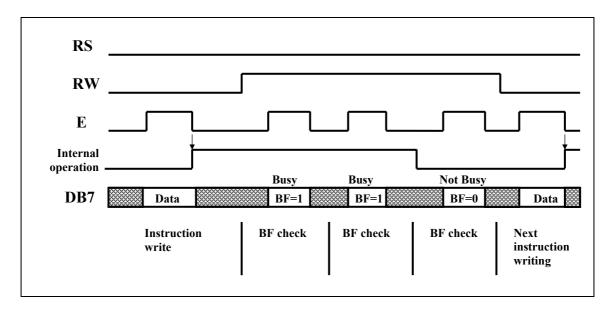

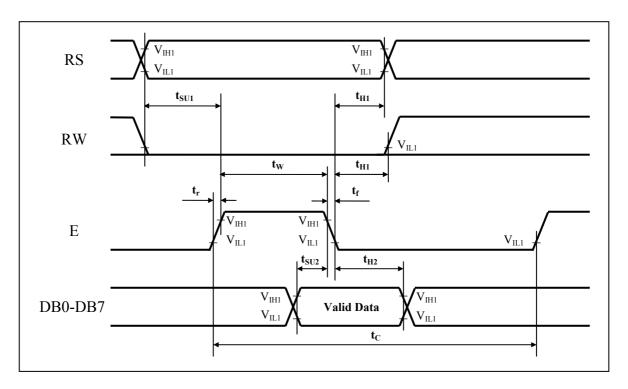

- In 8-bit mode (DL=1) all 8 bits are used. Data is strobed by E signal. Instructions start executing at the E fall, and BF sets to "1" (see Fig.2).

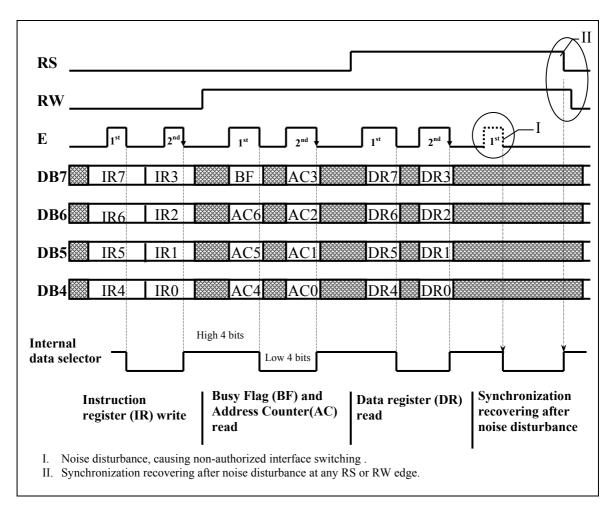

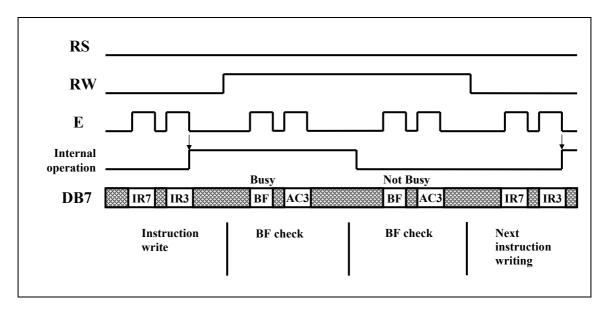

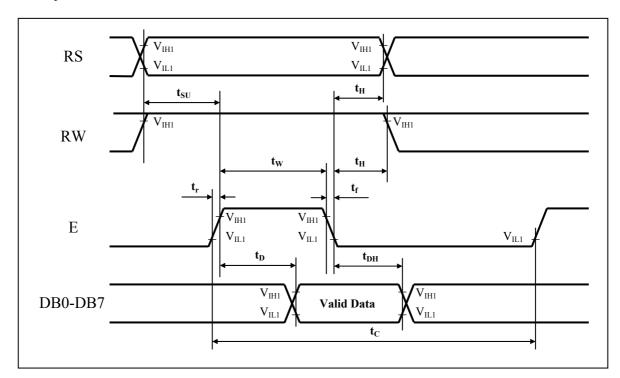

- In 4-bit mode (DL=0) only 4 bits (DB4-DB7) are used for exchanging data with MPU. DB0-DB3 bits are not used (pull up to VDD). In 4-bit interface bus mode, instructions and data are transmitted in two passes, corresponding to two E pulses (see figure 3). The four high order bits (DB4 to DB7 for 8-bit operation) are transferred before the four low order bits (DB0 to DB3). Internal data selector multiplexes high and low 4-bit data groups of register, switching at E fall. Instruction writing is complete and BF is set to "1" after the second E pulse. BF must be checked after the second E pulse of instruction.

Thus, each instruction should be accompanied with strictly two E pulses. If this condition is violated, then the sequence of data following may be broken. In this case the even and the odd 4-bit data groups of the register exchange their places. Single E pulse, owing to MPU synchronization loss or a noise influence, may break all further functioning of the controller.

To prevent this situation, the controller has the interface synchronization function, which provides the correct order of data following through 4-bit bus: any change of both RS or RW signals resets the selector of the data to the initial status (see figure 3). Also it is forbidden to change RS and RW status during submission of the instruction between E pulses.

#### 2.2. Standard and Extended modes

The An6866 has XMODE pad that allows to control access to some extended functions (see Table 2). The XMODE pad has internal pull up to VDD, therefore, if the XMODE pad is not connected, it has "1" state. The customer may select additional function set for both XMODE states (see part 3.5 "Controller mask option" and Order Form in Appendix 1).

Table 2. Standard and Extended modes

| XMODE    | Mode         | Characteristics                                                                                                                                                                                                 |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 or NC* | Standard     | Mode with standard functions available. Some of Extended functions                                                                                                                                              |

| 1 of NC  | (compatible) | may be enabled in Standard mode specified by Order Form.                                                                                                                                                        |

| 0        | Extended     | Mode with Extended functions, specified by Order Form:  • using of second CGROM page for 5x8 dot characters or 2 pages with software switching,  • underline cursor blinking,  • display inversion controlling. |

\*NC-not connected

Figure 2. Example of 8-bit interface operation.

Figure 3. Example of 4-bit interface operation.

#### 2.3. One- and two-line display

The controller can display characters in one or two lines. The number of lines is selected by Function Set instruction.

In one-line mode the controller displays characters from single DDRAM address range from 0 to 79 (4Fh). COM[1..8] lines are used for 5x8 dot characters, COM[1..11] lines are used for 5x11 dot characters.

In two-line mode the controller displays characters in two lines accordingly:

- DDRAM address range from 0 to 39 (27h) for the first line (COM[1..8]),

- DDRAM address range from 64 (40h) to 103 (67h) for the second line (COM[9..16]).

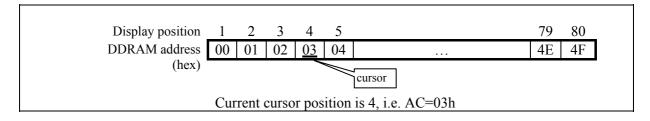

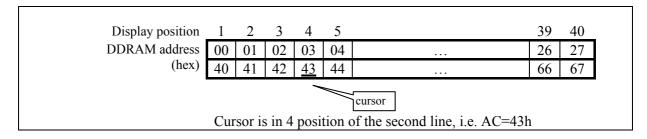

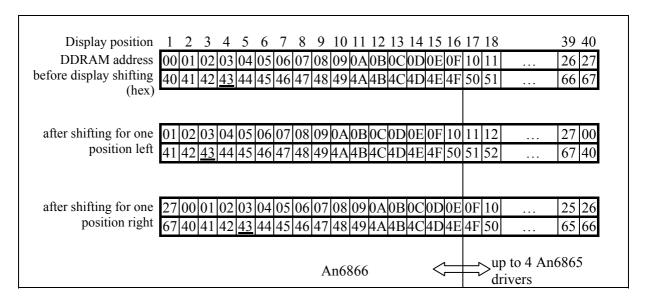

Correspondence between DRAM addresses and character positions in one-line mode and an example of cursor displaying in current display position, are shown in Fig. 4, 5.

Correspondence between DRAM address and character positions in two-line mode and example of cursor displaying in current display position, are shown in Fig. 6, 7.

#### 2.4. Address Counter (AC)

The current memory address (DDRAM and CGRAM), and cursor position are determined by Address Counter (AC). AC has reset to 0, setting a given state, increment and decrement functions.

AC resets to 0 when Display Clear and Return Home instructions are executed.

Desired AC value is set by Set DDRAM Address and Set CGRAM Address instructions. In this case the new address value is written into AC from Instruction Register (IR). Selection of memory type (DDRAM or CGRAM) is also made by these instructions.

Figure 4. One-line display without shifting.

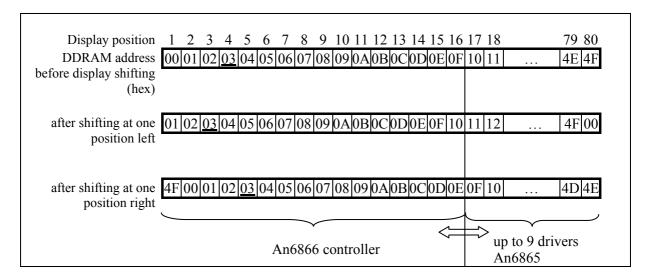

Figure 5. Display shifting in one-line mode.

Incrementing or decrementing of AC address value is made by following instructions:

- Memory read/write operations. Incrementing or decrementing is determined by ID bit of "Set Entry Mode" instruction (see part 2.10 "Instructions description").

- Cursor shift. This instruction also defines shift direction.

Count order of AC is defined by number of display lines (N bit of Function Set instruction) and accessed memory type (DDRAM or CGRAM).

While accessing to CGRAM, AC operates as complete 7-bit reversible counter without limitations (0 to 127). Only 6 bits are used for CGRAM addressing.

While accessing to DDRAM, the count order is following:

- for one-line mode:

- incrementing: 0, 1, 2, ... 78, 79, 0, 1, 2...

- decrementing: 0, 79, 78, 77, ... 2, 1, 0, 79...

- when AC value more than 79, the counter is incremented to 127 and then sets to 0.

- for two-line mode:

- incrementing: 0, 1, 2, ... 38, 39, 64, 65, ... 102, 103, 0, 1, ...

- decrementing: 0, 103, 102, ... 65, 64, 39, 38, ... 2, 1, 0, 103, ...

- when AC value more than 103, the counter is incremented to 127 and then sets to 0.

Figure 6. 2-line display without shifting.

Figure 7. Display shift in 2-line mode.

## 2.5. Start Address Counter and display shifting

The Start Address Counter is used for display shifting. This counter contain DDRAM address, which is used in the beginning of each COM-line scanning cycle to define the initial value of Refresh Counter. The Start Address Counter has a reset function and incrementing/decrementing functions.

The counter resets to the initial state when instructions Display Clear and Return Home are executed. After resetting, character line is displayed from 0 address of DDRAM.

The counter is incremented or decremented by Display Shift instruction according to shift direction. Count order is the same as for the AC counter (see part 2.4).

The counter has no address set function, and its state is not readable through MPU interface.

Correspondence between DDRAM address and displayed characters positions after left/right display shift in 1-line mode, is shown in Figure 5.

Correspondence between DDRAM address and displayed characters positions after left/right display shift in 2-line mode, is shown in Figure 7.

## 2.6. Timing Diagram

The internal controller timing diagram consists of periods, each one 5 clocks long. This is the time for transferring one character data (5-bit width) to output SEG register.

Each period contains three sequential phases of timing diagram:

- 1) phase of writing data to DDRAM/CGRAM and instruction execution,

- 2) phase of reading data from DDRAM/CGRAM to output data register of MPU interface.

- 3) phase of reading data from DDRAM/CGRAM/CGROM, and character displaying on the LCD (i.e. display refresh).

This solution provides complete time division between memory access processes, instructions execution, and display refresh. The MPU interface operates only with IR and DR registers with its own frequency independently from the slow controller timing diagram.

Phase 1 (2 clocks) provides MPU instructions execution, including instructions with memory accessing, using the address value stored in the AC. After completing data writing operation, the AC value is incremented or decremented if needed.

Phase 2 (1 clock) serves to read data from DDRAM/CGRAM to output data register DRout. Since the reading phase follows writing and instruction execution phase, data reading always occurs after address changing, if it took place during instruction execution. The following data reading instruction will allow to receive data from MPU interface, and data register will be filled with new data from the next memory address.

Phase 3 (2 clocks) provides display refresh and is used to transfer data from CGRAM/CGROM to the data shift register. The DDRAM character code, CGROM page number, and active COM number are used as CGRAM/CGROM address.

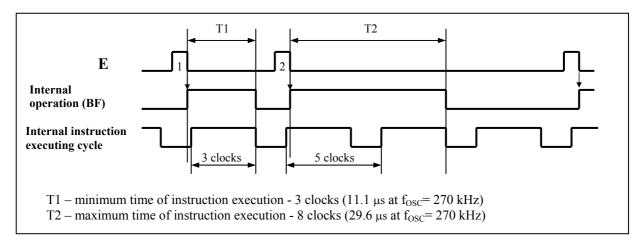

For execution of any instruction (except Display Clear) a complete pass of the 1st and 2nd phases is required. These two phases constitute Instruction Execution time, that is in a range from 3 to 8 clocks (see part 8.2). Display Clear instruction writes sequence of space characters (20h) into all 80 DDRAM addresses, which takes not more than 403 clocks.

There is possibility of express instructions execution under some additional conditions (see part 8.2).

Timing diagram of LCD depends on displaying mode.

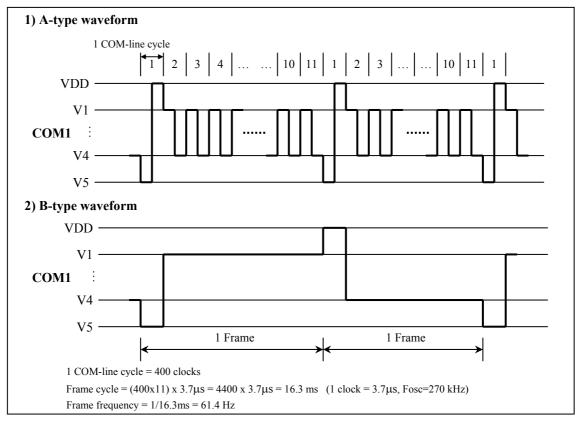

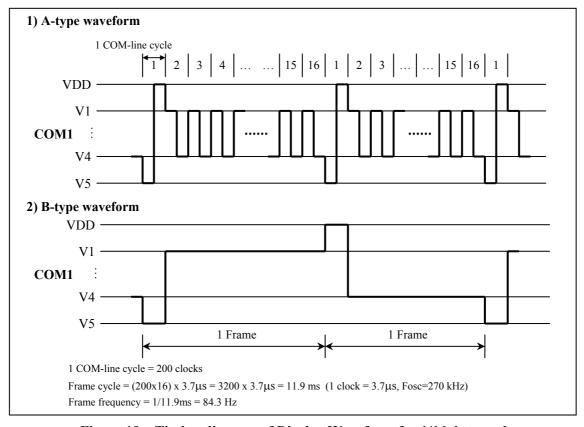

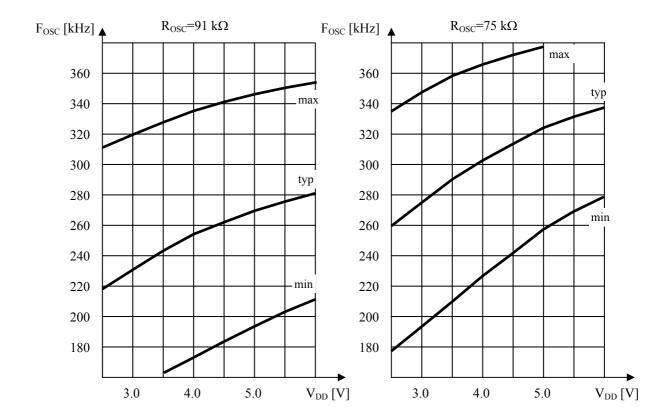

In 1-line mode 80 characters of 5 bit wide are displayed, therefore the period of active COM state is 80x5=400 clocks (1.48 ms at Fosc=270 kHz). Display refresh period is:

- for font 5x8 (i.e. 8 active COM lines): 8x1.48=11.84 ms, i.e. frame frequency is  $\approx 84.3$  Hz;

- for font 5x11 (i.e. 11 active COM lines): 11x1.48=16.28 ms, i.e. frame frequency is  $\approx 61.4$  Hz.

In 2-line mode 40 characters per each line can be displayed, therefore, the time of active COM state is 40x5=200 cycles (0.74 ms at Fosc=270 kHz). Display refresh period is 16x0.74=11.84 ms, i.e. frame frequency is  $\approx 84.3$  Hz.

Note that the controller always outputs data for a full character line, but the real number of displayed characters depends on the LCD size and number of connected extension drivers.

The controller timing diagram (except MPU interface) is closured to CLK2 clock grid, that is equal to oscillator frequency  $F_{OSC}$ , therefore, the controller timing diagram changes proportionally to  $F_{OSC}$  changing.

#### 2.7. Cursor/Character Blink control

The timer-divider with  $\approx$ 0.76 sec cycle at Fosc=270 kHz is used for cursor/character blinking. Cursor or character blinking position is defined by the AC.

#### 2.8. Power On Reset Function

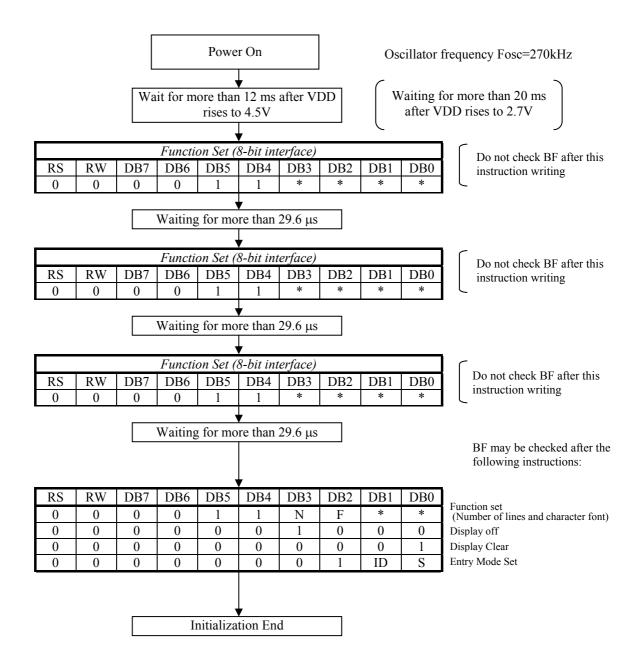

The internal reset circuit automatically initializes the An6866 when the power is on. BF is kept in the busy state until the initialization is finished. Time needed for reset procedure is up to 12 ms at Fosc=270kHz.

Reset procedure performs the following functions:

- Clear Display;

- Function Set:

DL=1, 8-bit interface\*),

N=0, 1-line display\*,

F=0, 5x8 dot character format\*);

P=0, Select of the first CGROM page, if software page control is enabled;

I=0, Inversion is off, if inversion control is enabled;

- Display on/off:

- D=0, Display is off,

- C=0, Cursor is off,

- B=0, Blinking is off;

- Entry Mode Set:

I/D=1, address increment mode,

S=0, display shift disable.

\*) Note: Initial state of DL, N, F bits of Function Set instruction can be defined by the Customer at the mask option order (see part 3.5. "Controller mask option").

The timer using for the initial reset procedure allows to obtain a stable result at VDD rising time up to 20 ms. However, if electrical characteristics of the device do not satisfy the conditions in part 6.3 "Power on conditions when using internal reset circuit", or if VDD voltage influence occurs, then the reset procedure may fail and cause an initialization error. In this case, it's possible to perform the initialization by instruction (see part 5.1 "Initialization by Instruction").

## 2.9. Instruction execution

An6866 has only two program accessible registers – instruction register (IR) and data register (DR). The number of register states and two control signals (RW – Read/Write and RS – Register Select) is determined by instruction set (Table 3). The instruction set may be divided into 4 categories:

- determination of the controller operation mode (display format, interface bus width etc.);

- setting the internal memory address and cursor position;

- transferring data between internal memory and MPU;

- service functions executing (Display Clear, Cursor Move etc.).

Usually, most of executing instructions are the data transferring instructions. To speed-up memory loading, the controller has an autoincrement memory address function. At that, the controller can also shift display automatically, which minimizes number of instructions, for example, in case the cursor

reaches the end of display.

For correct controller functioning, before each instruction writing, MPU must ensure that the previous instruction is completed and that interface registers are free. This can be made in two ways:

- By checking Busy Flag until its sets to 0. It is the most efficient way (see Figure 8 and 9).

- By time delay between instruction write, exceeding the maximum previous instruction execution time (see Table 3). It is a simple and slow method, but it is usable when data reading from the controller is never used (RW is fixed to 0). 4-bit interface synchronization function ensures maximum reliability of the controller operation with using only 6 interface lines (DB[7:4], E, RS).

Figure 8. Example of instruction writing with Busy Flag check in 8-bit interface mode.

Figure 9. Example of instruction writing with Busy Flag check in 4-bit interface mode.

Table 3. Instructions

|                                      |    |    |     |                 | Co                         | ode             |                 |                            |                            |                            | rable 3. In                                                                                                                       | Max exec.                 |

|--------------------------------------|----|----|-----|-----------------|----------------------------|-----------------|-----------------|----------------------------|----------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Instruction                          | RS | RW | DB7 | DB6             | DB5                        | DB4             | DB3             | DB2                        | DB1                        | DB0                        | Description                                                                                                                       | time<br>(Fosc=270<br>kHz) |

| Display Clear                        | 0  | 0  | 0   | 0               | 0                          | 0               | 0               | 0                          | 0                          | 1                          | Clear entire display and sets DDRAM address 0 in AC.                                                                              | 1,5 ms                    |

| Return Home                          | 0  | 0  | 0   | 0               | 0                          | 0               | 0               | 0                          | 1                          | _                          | Sets AC and Display shift counter to 0. DDRAM contents remain unchanged.                                                          | 29.6 μs                   |

| Entry Mode<br>Set                    | 0  | 0  | 0   | 0               | 0                          | 0               | 0               | 1                          | I/D                        | S                          | Sets cursor move direction<br>and specifies display shift<br>(enables only for writing).                                          | 29.6 μs                   |

| Display on/off<br>Control            | 0  | 0  | 0   | 0               | 0                          | 0               | 1               | D                          | C                          | В                          | Sets entire display (D), cursor (C) and blinking of cursor position character (B) on/off.                                         | 29.6 μs                   |

| Cursor or<br>Display Shift           | 0  | 0  | 0   | 0               | 0                          | 1               | S/C             | R/L                        | _                          | 1                          | Moves cursor (C) and shift display (S) without changing DDRAM contents left or right (R/L).                                       | 29.6 μs                   |

| Function Set                         | 0  | 0  | 0   | 0               | 1                          | DL              | N               | F                          | P* <sup>)</sup>            | I*)                        | Set Interface data length (DL), number of display lines (N), character font (F), current page number (P), and inversion mode (I). | 29.6 μs                   |

| Set CGRAM<br>Address                 | 0  | 0  | 0   | 1               | $\mathbf{A}_{\mathbf{CG}}$ | A <sub>CG</sub> | A <sub>CG</sub> | $\mathbf{A}_{\mathbf{CG}}$ | $\mathbf{A}_{\mathbf{CG}}$ | $\mathbf{A}_{\mathbf{CG}}$ | Sets CGRAM address. CGRAM data is send and received after this setting.                                                           | 29.6 μs                   |

| Set DDRAM<br>Address                 | 0  | 0  | 1   | A <sub>DD</sub> | A <sub>DD</sub>            | A <sub>DD</sub> | A <sub>DD</sub> | A <sub>DD</sub>            | A <sub>DD</sub>            | A <sub>DD</sub>            | Sets DDRAM address. DDRAM data is send and received after this setting.                                                           | 29.6 μs                   |

| Read Busy<br>Flag and<br>Address     | 0  | 1  | BF  | AC              | AC                         | AC              | AC              | AC                         | AC                         | AC                         | Reads BF and AC. This procedure do not blocking controller interface.                                                             | 0 μs                      |

| Write data to<br>CGRAM or<br>DDRAM   | 1  | 0  |     |                 | \                          | Writ            | e dat           | a                          |                            |                            | Writes data to CGRAM or DDRAM.                                                                                                    | 29.6 μs                   |

| Read data<br>from CGRAM<br>or DDRAM. | 1  | 1  |     |                 | ]                          | Reac            | l dat           | a                          |                            |                            | Reads data from CGRAM or DDRAM.                                                                                                   | 29.6 μs                   |

I/D: 1- Increment, 0- decrement;

DDRAM – Display Data RAM.

S: 1- display shift enable when write to DDRAM;

D: 1- display is on, 0- display is off;

C: 1- cursor is on, 0- cursor is off; CGRAM – Character Generator RAM.

B: 1- blinking is on, 0- blinking is off;

S/C: 1- Display shift, 0- cursor shift;  $A_{CG}$  - 6-bit CGRAM address. R/L: 1- Shift to the right, 0- Shift to the left;  $A_{DD}$  - 7-bit DDRAM address.

DL: 1-8-bit interface, 0-4-bit interface; AC – Address Counter for CGRAM and

DDRAM addressing.

N: 1- two-line display, 0- one-line display;

E: 1- font 5x11, 0- font 5x8; BF: 1 - Internally operating, E: 1- Second CGROM page, 0- First CGROM page; 0 - Instructions acceptable.

I: 1- Display inversion is on, 0- Display inversion is off;

indicates no effect.

<sup>\*)</sup> Extended function. Defined by Mask option (version) of controller and XMODE state

#### 2.10. Instructions

Display Clear

| RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Display Clear writes space code 20h (character pattern for character code 20h must be a blank pattern) into all DDRAM addresses. Then it sets DDRAM address 0 into the address counter, and returns the display to its initial status if it was shifted. In other words, the display disappears and the cursor or blinking goes to the left edge of the display (in the first line if 2 lines are displayed). It also sets I/D bit to 1 (increment mode) in entry mode. S bit of entry mode does not change.

Return Home

| RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

Return Home sets DDRAM address 0 into the Address Counter, and returns the display to its initial status if it was shifted. The DDRAM contents do not change. According to this settings the cursor returns to the initial position, i.e. to the left edge of the display (in the first line if display in the 2-line mode).

Entry Mode Set

| RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 0   | 0   | 0   | 0   | 0   | 1   | ID  | S   |

**I/D:** Incrementing (I/D=1) or decrementing (I/D=0) the DDRAM address by 1 occurs when a character code is written into or read from DDRAM.

The cursor or blinking moves to the right when incremented by 1 and to the left when decremented by 1. The same applies to writing and reading of CGRAM.

S: When the character code is being written to DDRAM, the entire display is shifted either to the right (I/D=0) or to the left (I/D=1) when S is 1. The display does not shift if S is 0.

If S is 1, it will seem as if the cursor does not move but the display does. The display does not shift when reading from DDRAM. Also, writing into or reading out from CGRAM does not shift the display.

Display on/off

| RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

**D:** The display is on when D is 1 and off when D is 0. When off, the display data remains in the DDRAM, but can be displayed instantly by setting D to 1.

When the display off, the repeating memory access for display refresh is absent and consumption current is decreased.

C: The cursor is displayed when C is 1 and not displayed when C is 0 in position corresponding to the AC. The cursor is displayed using 5 dots in the 8th line for 5x8 dot character font selection and in the 11th line for the 5x11 dot character font selection.

**B:** The character indicated by the cursor blinks when B is 1.

The cursor blinking mode is an extended function, and its use depends on chip version and XMODE state. For C=1 and B=1 case cursor blinking enable allows to obtain more effective view than character blinking when cursor is permanent on (see Table 4).

Cursor blink

Cursor blink disable  $\mathbf{C}$ В Cursor blink enable 0 0 Cursor is off, blink is off Cursor is off, blink is off 0 1 Cursor is off, character blink Cursor is off, character blink 1 0 Cursor is on, blink is off Cursor always on, blink is off 1 1

Table 4. Cursor displaying and character blinking modes

Cursor and Display Shift

| RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 0   | 0   | 0   | 1   | S/C | R/L | -   | -   |

Cursor and Display Shift instruction shifts the cursor position or entire display to the right or left without changing DDRAM data (table 5). This function is used to correct or search the display. When display is shifting, cursor position follows to the display move.

In a 2-line display, the cursor moves to the second line when it passes the 40th digit of the first line and vice versa. Note that the first and second display lines shift at the same time. When the display is shifted repeatedly, each line moves only horizontally. The characters in the second display line do not shift into the first line (see Figure 7).

The address counter (AC) contents will not change if the display shift is performed.

Cursor always on, character blink

Table 5. Cursor and Display Shift modes

| S/C | R/L | Description                                                   |

|-----|-----|---------------------------------------------------------------|

| 0   | 0   | Cursor moves left (AC decrement by 1)                         |

| 0   | 1   | Cursor moves right (AC increment by 1)                        |

| 1   | 0   | Display shift to left (start address counter increment by 1)  |

| 1   | 1   | Display shift to right (start address counter decrement by 1) |

Function Set

| RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 0   | 0   | 1   | DL  | N   | F   | P   | I   |

**DL:** Sets the interface data length. Data is transferred in 8-bit lengths (DB7-DB0) when DL=1, and in 4-bit lengths (DB7-DB4) when DL=0. When 4-bit length is selected, data must be transferred in two passes.

N: Sets the number of display lines.

**F:** Sets the character font.

|   |   |                  |           |            | Table 6. Tunction set modes                          |

|---|---|------------------|-----------|------------|------------------------------------------------------|

| N | F | Display<br>lines | Font size | Duty cycle | Notes                                                |

| 0 | 0 | 1                | 5x8       | 1/8        |                                                      |

| 0 | 1 | 1                | 5x11      | 1/11       |                                                      |

| 1 | * | 2                | 5x8       | 1/16       | displaying 2 lines of 5x11 characters is impossible. |

Table 6. Function set modes

**P:** Select of CGROM page: P=0 – the first page, P=1 – the second page. P bit allows to select CGROM page in the An6870 with the software support.

Two CGROM pages is an extended function in the An6866 controller. Possibility of the second page selection depends on chip version and XMODE state.

The following second CGROM page selections are possible:

- the second page is disabled, access to the first page at any case;

- page selection only by XMODE signal (fixed pages). In the standard mode the first page is selected by default (XMODE=1), in the extended mode (XMODE=0) the second page is selected. Software page selection is disabled, P bit has no effect;

- In the standard and/or extended mode software page selection is enabled, which allows to extend system functionality with MPU software support.

- **I:** Display inversion on/off. At I=1 black pixels become white (transparent). Inversion mode with back lighting allows to obtain "Information Board" view with bright characters on the black (dark) background.

Display inversion is an extended function, and its use depends on chip version and XMODE state.

The main features of Display Inversion function are the same as for Page Selection function (see above): disable, switching on/off by XMODE signal or software control.

Set CGRAM address

|    | •  | •   |     | MSB   |       |       |       |       | LSB   |

|----|----|-----|-----|-------|-------|-------|-------|-------|-------|

| 0  | 0  | 0   | 1   | AC[5] | AC[4] | AC[3] | AC[2] | AC[1] | AC[0] |

| RS | RW | DB7 | DB6 | DB5   | DB4   | DB3   | DB2   | DB1   | DB0   |

Set CGRAM address instruction writes 6-bit CGRAM address into the AC. After this instruction execution CGRAM is set as memory for reading/writing data.

Set DDRAM address

|    | I  | I   | MSB   | <u> </u> | <u> </u> |       | L 4   |       | LSB   |

|----|----|-----|-------|----------|----------|-------|-------|-------|-------|

| 0  | 0  | 1   | AC[6] | AC[5]    | AC[4]    | AC[3] | AC[2] | AC[1] | AC[0] |

| RS | RW | DB7 | DB6   | DB5      | DB4      | DB3   | DB2   | DB1   | DB0   |

The instruction Sets 7-bits DDRAM address into the AC. After this instruction execution DDRAM is set as memory for reading/writing data.

In 1-line mode (N=0) DDRAM address AC[6..0] must be in 00h-4Fh (0-79) range. In 2-line mode (N=1) DDRAM address AC[6..0] must be in 00h-27h (0-39) range for the first line and in 40h-67h (64-103) range for the second line.

CMID can be found in DDRAM address range 78h-7Fh (120-127, see part 3.4).

<sup>\* -</sup>no effect.

Read Busy Flag and Address

|    |    |     | MSB   |       |       |       |       |       | LSB   |

|----|----|-----|-------|-------|-------|-------|-------|-------|-------|

| 0  | 1  | BF  | AC[6] | AC[5] | AC[4] | AC[3] | AC[2] | AC[1] | AC[0] |

| RS | RW | DB7 | DB6   | DB5   | DB4   | DB3   | DB2   | DB1   | DB0   |

Read Busy Flag and Address instruction reads the BF indicating that the system is now internally executing the previous instruction. If BF=1, the internal operation is in process. The next instruction will not be accepted until BF is reset to 0. MPU must check the BF status before writing the next instruction. Simultaneously AC value at DB6-DB0 can be read by MPU. The address format is the same as for Set CGRAM/DDRAM Address instructions.

Note, that the AC can change during execution (i.e. BF=1) of some instructions, such as data read/write, cursor move etc. It is impossible to fix the moment of AC change relatively to E fall, but it has a fixed time interval till changing BF state to 0. This interval can be used for accurate estimation of oscillator frequency (see part 8.4). Read BF procedure is used only to determine the controller status and it is not an instruction, because it does not change the controller state (executing time is 0).

Write Data to CGRAM or DDRAM

| 1   0   D[7]   D[6]   D[5]   D[4]   D[3]   D[2]   D[1]   D[4] | Ī | 1 | 0 | D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0 |

|---------------------------------------------------------------|---|---|---|------|------|------|------|------|------|------|-----|

|                                                               | J |   |   | MCD  | D[v] | נים  | 2[.] | בובו | 2[2] | 2[1] | LOI |

The Write Data to CGRAM or DDRAM instruction writes 8-bit binary data to CGRAM or DDRAM.

The Address is determined by the previous specification of the CGRAM or DDRAM address setting. After a write, the address is automatically incremented or decremented by 1 according to the I/D bit of entry mode. Also it is possible to shift entire display backward when data writing to DDRAM (not CGRAM!), if this operation enabled by S bit of entry mode.

Read Data from CGRAM or DDRAM

| RS | RW | DB7  | DB6  | DB5  | DB4  | DB3  | DB2  | DB1  | DB0  |

|----|----|------|------|------|------|------|------|------|------|

| 1  | 1  | D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|    |    | MSB  |      |      |      |      |      |      | LSB  |

The Read Data from CGRAM or DDRAM instruction reads 8-bit binary data D[7..0] from CGRAM or DDRAM at AC address into data bus interface.

Reading data from DDRAM/CGRAM is realized in two stages. First, after any instruction execution CGRAM/DDRAM data is put into output data register (DRout). This is guaranteed that data in the DRout is always from the last address, even if it has been changed during the last instruction execution. At high E level data from the DRout is transferred to data bus interface. Then at E fall the controller performs AC incrementing or decrementing during instruction execution according to I/D bit of entry mode. At that, reading data from next memory address into DRout is performed.

Automatical AC incrementing or decrementing imply that the last writed data cannot be verified immediately by the Read instruction. If the verification is needed, executing the address set or cursor move instructions must be performed before reading data.

When data reading, the display is not shifting.

#### 3. INTERNAL CONTROLLER MEMORY

#### 3.1. Display Data RAM (DDRAM)

DDRAM stores display data represented in 8-bit character codes.

In read/write mode, access to DDRAM is made at the current AC address. DDRAM addressing depends on the number of display lines:

- in 1-line mode address, range from 0 to 79 is used,

- in 2-line mode, the following address ranges are used (see part 2.4):

- o 0-39 for the first line,

- o 64-103 for the second line.

At display refresh, the code read from the DDRAM combined with the current COM number and page number is used to generate CGROM/CGRAM address. Character pattern information from CGROM/CGRAM is used for displaying characters on LCD.

## 3.2. Character Generator ROM (CGROM)

CGROM pattern is programmed by mask option during manufacture. There are 2 available font sizes: 5x8 and 5x11 dots.

8-bit character code allows to display simultaneously up to 256 characters from the character pattern table (see Appendix 3). Each character code is composed from 4-bit column address and 4-bit row address. 240 or 248 codes may be assigned to the CGROM, correspondingly 16 or 8 codes remain for the CGRAM.

The CGROM consists of 248 character cells of 5x16 size. In each cell it is possible to place two 5x8 dot characters or one 5x11 dot character. The 5x8 dot character set forms two CGROM pages, accessible by P bit of Function Set instruction and XMODE signal (depends on the controller mask option). 5x11 dot characters can not be coded in two pages, therefore, they have only one set and they are displayed equally for both pages.

There are some differences in address generating for 5x8 dot and 5x11 dot characters (see tables 7 and 8). Therefore, the controller contains special circuits - comparators of 4 high order bits of the address that defines code range for two-page table region with 5x8 characters: Amin ÷ Amax.

Inside the Amin÷Amax range it is possible to select 5x8 character with P bit (page number) and XMODE state. Outside the Amin÷Amax range it is possible to select characters only from one page, which allows to code one set of 5x8 or 5x11 characters.

Since only 4 high order bits of the address (or character code) are compared, the table may be divided into one-page and two-page parts, multiplicity equals strictly 16 (entire column). For example, for S00 coding Amin=1h and Amax=Dh, which allows to code 208 5x8 characters per each of two pages (10h-DFh), and 32 5x11 characters (E0h-FFh).

For the Customer's new mask option and page control possibilities see part 3.5 "Controller mask option", for released options see Appendix 3.

Note, that in 1-line mode with 1/8 duty (N=0  $\mu$  F=0), and in 2-line mode, 5x11 dot characters are displayed in a truncated form: only 8 upper COM-lines are displayed. On the other hand, in 1/11 duty mode (i.e. at 11 active COM-lines) 5x8 characters at two-page coding are supplemented with spaces in 9, 10 and 11 COM-lines, thus, providing correct displaying though character presence on the next page (see Table 8).

The An6866 also has a capability to readdress 08h-0Fh codes to CGROM, which is assigned for replication of 00h-07h CGRAM codes. The corresponding function is enabled by the controller mask option according to the Customer's request (see part 3.5). In this case, maximum CGROM capacity is up to 248 characters at each of two pages, 496 characters in two pages in 08h-FFh code range.

#### 3.3. Character Generator RAM (CGRAM)

User can write into CGRAM his own character patterns: 8 characters 5x8 dots or 4 characters 5x11 dots. Correspondence of CGRAM addresses and character codes is shown in Table 9 for 5x8 dots characters and in Table 10 for 5x11 dot characters.

A CGRAM cell, which contains information about one 5x8 character occupies 8 bytes. Every byte contains information about one character line; only 5 low order bits (D4-D0) are used for displaying, 3 high order bits (D7-D5) are not used. CGRAM size is 64 bytes; it is possible to write 8 characters 5x8 dots.

When writing 5x11 characters, each character occupies two 8-byte CGRAM cells. In the second cell 9, 10, 11 character lines are coded. Information in the next 5 bytes is not displayed and may contain general purpose data. CGRAM 5x11 dot character codes will be numbered every other one in 00h-07h code range. For example, if the first character is written in CGRAM from cell 0 occupying cells 0 and 1, it is possible to use codes 00h, 02h, 04h and 06h to display such 4 characters.

*Note*: When using 5x11 font mode, 5x8 characters must also be coded in 11 lines with spaces in 9, 10, and 11 character lines, because function of automatical space filling, used in 2-page CGROM code table, does not work with CGRAM.

In the standard chip version 16 codes are used for CGRAM. CGRAM characters repeat twice – for codes 00h-07h and 08h-0Ah. At that, the D3 bit of character code is not used for CGRAM addressing.

For advanced possibilities, the D3 bit (address A7, see Table 9) may be used for CGROM/CGRAM address sharing. Codes 00h-07h remain for CGRAM. 8 additional codes (08h-0Fh) pass to CGROM, thus, increasing the total character numbers up to 248.

In Tables 9 and 10 there are complete addresses used to address CGROM/CGRAM, and corresponding AC addresses used for access through the MPU interface.

**CGROM Address** Data Character code P COM[1..8]  $\mathbf{A}_3$  $\mathbf{A_2}$  $\mathbf{A}_{\mathbf{0}}$  $O_4$  $\mathbf{Q}_3$  $Q_2$   $Q_1$  $\mathbf{Q}_0$  $A_{11} A_{10}$  $\mathbf{A}_{9}$  $A_7$  $A_5$  $A_4$  $\mathbf{A}_{1}$  $\mathbf{A_8}$  $A_6$ First page ← cursor position Second page

Table 7. CGROM addressing and 5x8 dot character coding

Notes:

- 1. Character code, corresponding to the addresses  $A_{11}$ - $A_4$ , is chosen from DDRAM (D7-D0) according to the character position on the display.

- 2. P (address A<sub>3</sub>) –CGROM page number.

- 3. Addresses A<sub>2</sub>-A<sub>0</sub> –COM[1..8]-line number.

- 4. Pixel is "on" corresponding to "1" in CGROM.

| Table 8 | <b>CGROM</b> | addressing | and 5x11 | dot character | coding |

|---------|--------------|------------|----------|---------------|--------|

|         |              |            |          |               |        |

|                 |                 |     |                |                | ROM   |                |        | aares          | 531115         | una s            | XIIC  |       |       |                |                  | 4111 <u>5</u> |                                                    |

|-----------------|-----------------|-----|----------------|----------------|-------|----------------|--------|----------------|----------------|------------------|-------|-------|-------|----------------|------------------|---------------|----------------------------------------------------|

|                 |                 | C   | harac          |                |       |                |        |                | COM            | [111             | 1     |       |       | Dat            | a                |               |                                                    |

| A <sub>11</sub> | A <sub>10</sub> | A9  | A <sub>8</sub> | $\mathbf{A}_7$ | $A_6$ | A <sub>5</sub> | $A_4$  | $\mathbf{A_3}$ | $\mathbf{A_2}$ | $\mathbf{A}_{1}$ | $A_0$ | $Q_4$ | $Q_3$ | $\mathbf{Q}_2$ | $\mathbf{Q}_{1}$ | $Q_0$         |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 0              | 0                | 0     | 1     | 0     | 0              | 0                | 0             |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 0              | 0                | 1     | 1     | 0     | 0              | 0                | 0             |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 0              | 1                | 0     | 1     | 0     | 1              | 1                | 0             |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 0              | 1                | 1     | 1     | 1     | 0              | 0                | 1             | First page                                         |

|                 |                 |     |                |                |       |                |        | 0              | 1              | 0                | 0     | 1     | 0     | 0              | 0                | 1             | or                                                 |

|                 |                 |     |                |                |       |                |        | 0              | 1              | 0                | 1     | 1     | 0     | 0              | 0                | 1             | Second page                                        |

|                 |                 |     |                |                |       |                |        | 0              | 1              | 1                | 0     | 1     | 1     | 1              | 1                | 0             |                                                    |

| 0               | 1               | 1   | 0              | 0              | 0     | 1              | 0      | 0              | 1              | 1                | 1     | 0     | 0     | 0              | 0                | 0             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 0              | 0                | 0     | 0     | 0     | 0              | 0                | 0             | At 1/11duty 5x8 charac-                            |

|                 |                 |     |                |                |       |                |        | 1              | 0              | 0                | 1     | 0     | 0     | 0              | 0                | 0             | ter is supplemented with "0" in 9, 10 and 11 lines |

|                 |                 |     |                |                |       |                |        | 1              | 0              | 1                | 0     | 0     | 0     | 0              | 0                | 0             | J←cursor position                                  |

|                 |                 |     |                |                |       |                |        | 1              | 0              | 1                | 1     | *     | *     | *              | *                | *             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 1              | 0                | 0     | *     | *     | *              | *                | *             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 1              | 0                | 1     | *     | *     | *              | *                | *             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 1              | 1                | 0     | *     | *     | *              | *                | *             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 1              | 1                | 1     | *     | *     | *              | *                | *             |                                                    |

|                 | •••             | ••• | •••            | • • • •        |       | ••••           | •• ••• | •••            |                | •••              |       | •••   | • ••  | • • • •        | •••              |               |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 0              | 0                | 0     | 0     | 0     | 0              | 0                | 0             |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 0              | 0                | 1     | 0     | 0     | 0              | 0                | 0             |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 0              | 1                | 0     | 0     | 1     | 1              | 0                | 1             |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 0              | 1                | 1     | 1     |       | 0              | 1                | 1             |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 1              | 0                | 0     | 1     | 0     | 0              | 0                | 1             |                                                    |

|                 |                 |     |                |                |       |                |        | 0              | 1              | 0                | 1     | 1     | 0     | 0              | 0                | 1             |                                                    |

|                 |                 |     |                |                |       | •              |        | 0              | 1              | 1                | 0     | 0     | 1     | 1              | 1                | 1             |                                                    |

| 1               | 1               | 1   | 1              | 0              | 0     | 0              | 1      | 0              | 1              | 1                | 1     | 0     | 0     | 0              | 0                | 1             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 0              | 0                | 0     | 0     | 0     | 0              | 0                | 1             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 0              | 0                | 1     | 0     | 0     | 0              | 0                | 1             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 0              | 1                | 0     | 0     | 0     | 0              | 0                | 0             | ←Cursor position                                   |

|                 |                 |     |                |                |       |                |        | 1              | 0              | 1                | 1     |       |       |                | *                |               |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 1              | 0                | 0     | *     | *     | *              | *                | *             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 1              | 0                | 1     | *     | *     | *              | *                | *             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 1              | 1                | 0     | *     | *     | *              | *                | *             |                                                    |

|                 |                 |     |                |                |       |                |        | 1              | 1              | 1                | 1     | *     | *     | *              | *                | *             |                                                    |

Notes:

- 1. Character code, corresponding to the addresses A<sub>11</sub>-A<sub>4</sub>, is chosen from DDRAM (D7-D0) according to the character position on the display.

- 2. Addresses  $A_3$ - $A_0$  COM[1..11]-line number.

- 3. 5x8 characters from two-page area (Amin÷Amax) are supplemented with "0" in COM[9..11]-lines.

- 4. Characters from one-page area out of the address range (Amin÷Amax) occupy all 11 lines.

- 5. Data in COM[12..16]-lines are not displayed (sign \*).

- 6. Pixel is "on" corresponding to "1" in CGROM.

**CGRAM Address CGRAM** selection sign Data Character code COM[1..8] AC<sub>5</sub> AC<sub>4</sub> AC<sub>3</sub>  $AC_2$  $AC_1 \quad AC_0$ **MSB LSB**  $Q_7 Q_6 Q_5 Q_4 Q_3 Q_2 Q_1 Q_0$  $\mathbf{A}_{1}$  $A_5$  $A_0$ First character ← cursor position Second character

Table 9. CGRAM addressing for 5x8 dot characters

Notes:

1. Character code, corresponding to the address  $A_{11}$ - $A_4$ , is chosen from DDRAM (D7-D0) according to the character position on the display.

← cursor position

- 2. Addresses  $A_{11}$ - $A_7$  indicate CGRAM selection for display refresh ( $A_{11}$ - $A_7$ =0000\*). Address  $A_7$  is not usually used, that means selection of CGRAM for codes 00h-0Fh. However, it may be additionally determined, at that,  $A_7$ =0 will mean selection of CGRAM (8 codes 00h-07h),  $A_7$ =1 selection of CGROM (8 additional codes 08h-0Fh, totally 248 CGROM characters).

- 3. Addresses A<sub>6</sub>-A<sub>4</sub> CGRAM character code (3 addresses, 8 characters 5x8).

- 4. Address  $A_3$  not used to display 5x8 characters.

- 5. Addresses  $A_2$ - $A_0$  COM[1..8]-line number.

- 6. AC<sub>5</sub>-AC<sub>0</sub> the address counter (AC) bits while read/write data operations.

- 7. Pixel is "on" corresponding to "1" in CGROM.

- 8. CGRAM  $Q_7$ - $Q_5$  lines are not displayed and can be used as conventional memory.

**CGRAM** selection sign **CGRAM Address** Data Character code COM[1..11]  $AC_3 \quad AC_2 \quad AC_1 \quad AC_0$ **MSB** LSB AC<sub>5</sub> AC<sub>4</sub>  $A_5$  $\mathbf{A}_{2}$  $\mathbf{A}_{\mathbf{0}}$  $Q_7 \ Q_6 \ Q_5 \ Q_4 \ Q_3 \ Q_2 \ Q_1 \ Q_0$  $A_6$  $\mathbf{A}_{1}$ First character ← cursor position Second character ← cursor position

Table 10. CGRAM addressing for 5x11 dot characters

Notes:

- 1. Character code, corresponding with addresses A<sub>11</sub>-A<sub>4</sub>, is chosen from DDRAM (D7-D0) according to character position on display.